# Influence of the edge effects on the MESFET transistor characteristics

Saida Mellal, Cherifa Azizi, Mourad Zaabat and Toufik Ziar

Faculty of exact sciences and natural and life sciences

Active Devices and Materials Laboratory

Larbi Ben M'Hidi university, Oum El Bouaghi -Algérie-

saida\_mellal@yahoo.fr

The Received date: May 25, 2014; revised date: December 10, 2014; accepted date: December 21, 2014

## Abstract

A two-dimensional numerical analysis is presented to investigate the field effect transistor characteristics. Our main aim in these sheet related on the one hand to the optimization of a two dimensional (2D) analytical model for the static characteristics of short gate-length GaAs MESFET's, this model takes into account the different physical specific phenomena of the device, and on the other hand to study the influence of the effect edge on the variation of some intrinsic elements (transconductance and drain conductance). The model suggested has enables to us to calculate and trace the different series from curves. The results obtained are well represented and interpreted.

Key words: MESFET, Two-dimensional modeling, Edge effects, Characteristics (I-V, Gm, Gd)

## 1. Introduction

With current technological progress, the submicron components are then more powerful, but the complexity of their function increases as soon as dimensions are reduced. The development or the improvement of new dies of components requires means for the modelling, the realisation and the characterisation. It is thus very significant to predetermine the characteristic of the component, physical-modelling finds here one of its principal application.

Taking into account the complexity of the operation of a field-effect transistor to submicron gate, the designer of the components must know the influence of the technological parameters, so that this one can envisage their influence on the behaviour of the device. So in this paper the edge effects have been taken into account and their influence on the current voltage characteristics, the transconductance and drain conductance are investigate.

In this work we have made two-dimensional simulation of component with field effect's considering the effects of edge and the parasitic resistances of source and of drain, of our structure.

## 2. Model and voltage-current (I-V) equations

In the submicron MESFET, the channel potential cannot be entirely controlled by the gate bias and will be shifted by the penetration of lateral electric field. Therefore

the lateral field distribution at the gate edges plays an important role for the short channel effects.

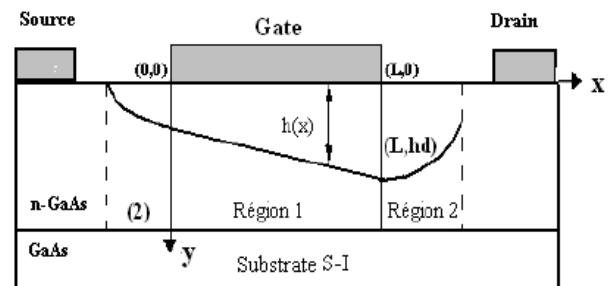

Thus solution for 2D Poisson's equation satisfying suitable boundary conditions is required to model the short channel effect. A simplified self aligned GaAs MESFET is shown in Fig.1 [1], over which Poisson's equation is solved for the potential distribution  $V_c(x,y)$ , where 'L' is the gate length. 'a' is the thickness of the active layer.

In order to avoid the problems resulting from different surface boundary conditions, the n-GaAs layer is assumed to contact directly to the gate metal, and the absorption of electric field by the depletion charges near the source/drain is not taken into account.

Fig. 1. Schematic diagram of a self-aligned GaAs MESFET

### 2.1. Calculation of the potential in the channel and the electrical field

The 2D Poisson equation for the depletion region, assuming complete depletion, is

$$\nabla^2 V_c(x, y) = \frac{d^2 V_c}{dx^2} + \frac{d^2 V_c}{dy^2} = -\frac{q}{\epsilon} N_d(y) \quad (1)$$

$V(x, y)$  is the electrostatic potential,  $q$  is electron charge,  $\epsilon$  is the dielectric permittivity of GaAs semiconductor,  $N_d(y)$  is the doping concentration, The doping is considered to be uniform, with the doping concentration  $N_d$ .

According to the superposition technique [2], (1) can be resolved as

$$V_c(x, y) = V(x, y) + V_l(x, y) \quad (2)$$

Where  $V(x, y)$  is the solution of Poisson's equation (3) for the MESFET structure in one dimension along y-axis near the mid of the channel (region 1). It is this potential profile that would result if the device were completely unaffected by lateral electric fields from the source and the drain;  $V_l(x, y)$  is the 2D potential function responsible for the short channel effects [6], it represents the voltage brought by the overflow of the depletion region at the drain and source sides (region2):

$$\frac{d^2 V(x, y)}{dy^2} = -\frac{q}{\epsilon} N_d(y) \quad (3)$$

$$\frac{d^2 V_l}{dx^2} + \frac{d^2 V_l}{dy^2} = 0 \quad (4)$$

To find solution of these equations (3) and (4), we used the boundary conditions expressed as [3]:

$$V(x, y)|_{y=0} = Vg - Vbi \quad (5)$$

$$\left. \frac{dV(x, y)}{dy} \right|_{y=a} = 0 \quad (6)$$

$$V_c(L, y) = V_{bi} + V_d, \quad V_l(L, y) = V_{bi} + V_d - V(y) \quad (7)$$

$$\frac{dV_c(x, a)}{dy} = 0, \quad \frac{dV_l(x, a)}{dy} = 0, \quad \frac{dV_c(L, a)}{dx} = E_s \quad (8)$$

Where  $V_{bi}$  is the potential of built-in schottky-barrier,  $V_g$  is the applied gate-source voltage,  $V_d$  is the applied drain-source voltage and  $E_s$  is the saturation electric field.

Using (5) and (6) in (3), the solution of 1D Poisson's equation is based on the fact that the depletion layer thickness under the gate,  $h(x)$  is a slowly varying function in the channel.

The channel potential is obtained by integration limits with  $y = h(x)$

$$V(x, y) = \frac{q}{\epsilon} \int_0^{h(x)} y N_d(y) dy + Vg - Vbi \quad (9)$$

So :

$$V(x) = \frac{q N_d}{2\epsilon} h^2(x) + Vg - Vbi \quad (10)$$

$$h(x) = \sqrt{\frac{2\epsilon(V(x) + V_{bi} - V_g)}{q N_d}} \quad (11-1)$$

Where  $V(x)$  is the potential of the neutral channel with  $V(0) = 0$  at the source-end and  $V(L) = V_d$  at the drain-end. So that the depletion widths at the source and drain ends given respectively by :

$$h_s = \sqrt{\frac{2\epsilon(V_{bi} - V_g)}{q N_d}} \quad (11-2)$$

$$h_d = \sqrt{\frac{2\epsilon(V_d + V_{bi} - V_g)}{q N_d}} \quad (11-3)$$

To determine the two-dimensional term  $V_l(x, y)$  in the frame of boundary condition Eqns (4,7,8), the solution suggested in this study may be written in the following form[1,6].

$$V_l(x, y) = \alpha [Sinh(k(L - x)) + Sinh(kx)] Sin(ky) \quad (12)$$

$$k = \frac{\pi}{2a}$$

$$\text{Where: } \alpha = \frac{2aE_s}{\pi(\cosh(kL) - 1)}$$

Following (2), (10) and (12) the expression for the two dimensional potential of the channel under the gate with edge effects, is given as follows:

$$V_c(x, y) = \frac{q N_d}{2\epsilon} h^2(x) + Vg - Vbi + V_l(x, y) \quad (13)$$

## 2.2. Current-voltage characteristics I - V

In order to calculate the drain current expression as a function of the drain voltage for different values of the gate voltage, we use the following hypothesis:

- We neglect the current in the Y axis; this approximation is valid for the short gate components.

- The channel is divided in two regions according to the value of the electric field.

- The analytical expression of the variations of the electron mobility with electric field [4] is given by:

- For the low electric fields:  $E < E_s$

$$\mu = \mu_0 \quad (14-1)$$

- For the electric fields higher than  $E_s$ : ( $E \geq E_s$ )

$$\mu = \frac{\mu_0}{\left[ 1 + \left( \frac{E - E_0}{E_s} \right)^2 \right]^{1/2}} \quad (14-2)$$

where:  $E$  is the electric field,  $\mu_0$  is the low mobility, and  $E_s$  is a critical field ( $E_s = 3, 5$  kV/cm for the GaAs [4]).

The density of the current is given by:

$$j_x = \sigma(x, y, z) E_x \quad (15)$$

$$j_x = q\mu N_d \cdot E_x = -q\mu N_d \cdot \frac{dV_c(x, y)}{dx} \quad (16)$$

The drain current  $I_d$  counted positively in the sense drain source is obtained by integrating  $J_x$  across the conductor section of the channel:

$$I_d = - \int_0^Z \int_{h(x)}^a j_x d_y d_z = -Z \int_{h(x)}^a j_x d_y \quad (17)$$

Using single integrals, the current expression is obtained by relation:

$$I_d = \frac{(qN_d)^2 Z \mu}{\epsilon L} \left[ \frac{a}{2} (W_d^2 - W_s^2) - \frac{1}{3} (W_d^3 - W_s^3) \right] \quad (18)$$

$W_s$  and  $W_d$  are the two dimensional widths of the depletion layer side source and drain respectively. They are calculated by considering firstly the one-dimensional approximation  $h(x)$  then we have added the **corrective term**  $V_l(x, h(x))$  which results with the two dimensional analysis ( equation 12 ) [3].

So that equations (11-1, 11-2, 11-3) becomes as follows:

$$W(x) = \sqrt{\frac{2\epsilon(V(x) + V_{bi} - V_g - V_l(x, h(x)))}{qN_d}} \quad (19-1)$$

$$W_s = \sqrt{\frac{2\epsilon(V_{bi} - V_g - V_l(0, h_s))}{qN_d}} \quad (19-2)$$

$$W_d = \sqrt{\frac{2\epsilon(V_d + V_{bi} - V_g - V_l(L, h_d))}{qN_d}} \quad (19-3)$$

By deferring two expressions (19-2) and (19-3) in equation (18) the general equation of current becomes:

### Linear regime

This regime exists as the electric field in the channel is low and the electron mobility is equal to  $\mu_0$ . Expression of the drain current in this regime can be written as:

$$I_d(V_d, V_g) = I_p \left[ \frac{V_d - (V_l(L, h_d) + V_l(0, h_s))}{V_p} - \frac{2}{3} \left( \frac{V_d + V_{bi} - V_g - V_l(L, h_d)}{V_p} \right)^{3/2} \right] + \frac{2}{3} \left( \frac{V_{bi} - V_g - V_l(0, h_s)}{V_p} \right)^{3/2} \quad (20)$$

$$\text{Where: } I_p = \frac{(qN_d)^2 Z \mu_0 a^3}{2\epsilon L} \quad \text{and: } V_p = \frac{qN_d}{2\epsilon} a^2$$

### Saturation regime

Drain voltage increases when the electric field in the channel increases beyond  $E_s$ . The electron mobility is given by (14-2).

The saturation value  $V_{dsat}$  is taken as the voltage where the conduction channel depleted near the drain. So:

$$V_{dsat} = V_p + V_g - V_{bi} + V_l(L, h_d) \quad (21)$$

The simplified expression for the saturation drain current is:

$$I_{dsat} = I_p \left[ \frac{1}{3} - \left( \frac{V_{bi} - V_g - V_l(0, h_s)}{V_p} \right) + \frac{2}{3} \left( \frac{V_{bi} - V_g - V_l(0, h_s)}{V_p} \right)^{3/2} \right] \quad (22)$$

$$\text{With: } I_p = \frac{(qN_d)^2 Z \mu a^3}{2\epsilon L}$$

### 3. Transconductance and drain conductance

The expression of  $I_d$  is used to calculate the two basic parameters of the transistor, which are the transconductance  $g_m$  and the channel conductance  $g_d$  more commonly known as drain conductance.

- The transconductance is the expression of the control mechanism of a transistor: it represents the variation of the current in the channel modulated by the gate voltage at constant drain-source voltage [5].

### In the Linear regime

$$g_m = \frac{Z\mu_0}{L} (2\epsilon q N_d)^{1/2} \left[ (V_d + V_{bi} - V_g - V_l(L, h_d))^{1/2} - (V_{bi} - V_g - V_l(0, h_s))^{1/2} \right] \quad (23)$$

### In the saturation regime

$$g_{msat} = \frac{Z\mu}{L} (2\epsilon q N_d)^{1/2} \left[ (V_p)^{1/2} - (V_{bi} - V_g - V_l(0, h_s))^{1/2} \right] \quad (24)$$

- The conductance reflects the resistance of the channel: it is the variation of the drain current according to the  $V_d$  voltage variation, with constant polarization of the gate.

### In the Linear regime

$$g_d = \frac{Z\mu_0}{L} (2\epsilon q N_d)^{1/2} \left[ (V_p)^{1/2} - (V_d + V_{bi} - V_g - V_l(L, h_d))^{1/2} \right] \quad (25)$$

### In the saturation regime

$$\text{The conductance is perfectly zero, } g_{dsat} = 0 \quad (26)$$

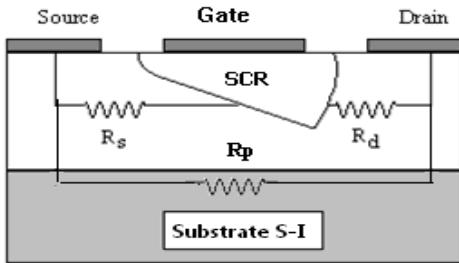

#### 4. Influence of parasitic resistances

The characteristics that we have presented are those of the internal or intrinsic sizes ( $I_d$ ,  $V_d$ ,  $V_g$ ) to obtain the external or extrinsic characteristics of the component ( $I_d$ ,  $V_d$ ,  $V_g$ ), it is enough to take into account the effect of parasitic resistances to access of source  $R_s$  and drain  $R_d$ , and also the effect of  $R_p$  parallel resistance to the canal on the values of polarization voltages [4] as shown in figure 2.

Figure 2 : Parasitic resistances in the MESFET GaAs.

To obtain the real expressions of characteristics  $I_d$ ,  $g_d$  and  $g_m$ , it is enough to replace the intrinsic terms by the extrinsic terms in all the preceding relations:

$$\begin{aligned} I_d &= I_{ds} - (V_{ds} / R_p) \\ V_d &= V_{ds} - (R_s + R_d) I_d \\ V_g &= V_{gs} - R_s I_d \end{aligned} \quad (27)$$

#### 5. Results and discussions

Software of simulation based on the expressions established in the preceding paragraphs is realized in **Matlab**, The study was carried out on a submicron gate GaAs MESFET transistor which parameters gathered in the table (1).

| L (μm)                | a(μm)               | Z(μm)  | μo(m²/Vcm) |

|-----------------------|---------------------|--------|------------|

| 1                     | 0,153               | 100    | 0,2800     |

| Nd(At/m³)             | Vs(m/s)             | Vbi(V) | Vp(V)      |

| 1,17 10 <sup>23</sup> | 3.6 10 <sup>5</sup> | 0,85   | 1.93       |

Table (1): GaAs MESFET transistor parameters

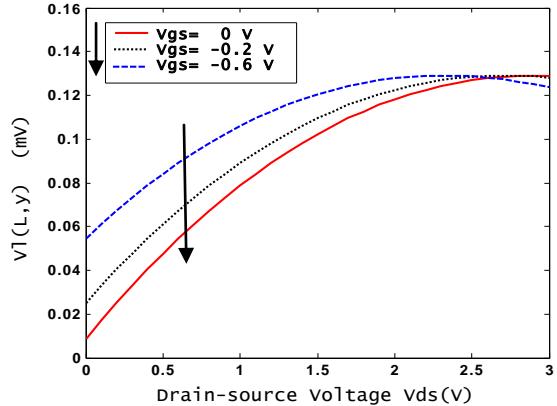

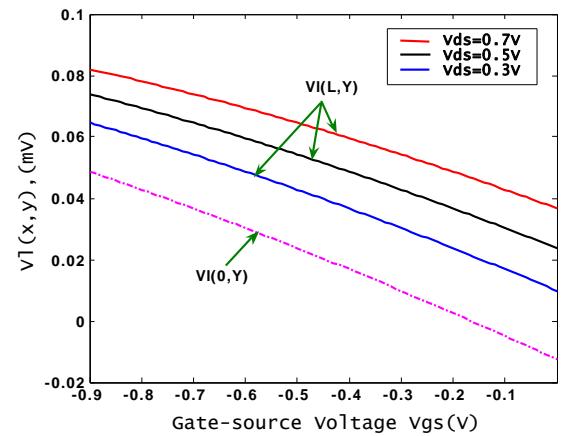

Figures (3) and (4) shows the variation of the potential  $V(x,y)$ , which result on the two dimensional analysis (Eqn12). Where the voltages  $V(0,hs)$  and  $V(L,hd)$  are plotted as a function of drain and gate bias .

Figure 3: Variations  $V(L,hd)$  voltages according to drain bias

Figure 4: Variations  $V(0,hs)$  and  $V(L,hd)$  voltages according to gate bias

In these figures, we noticed that the voltages  $V(0,hs)$  and  $V(L,hd)$  of the edge effects are found to be positive and both these quantities increases gradually as the absolute value of the gate voltage "Vgs" increases, and also with the increase of the voltage drain "Vds".

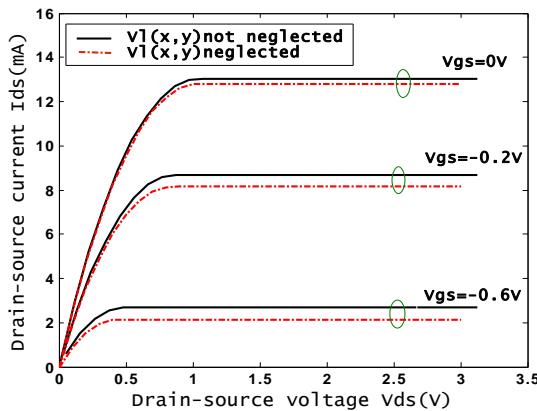

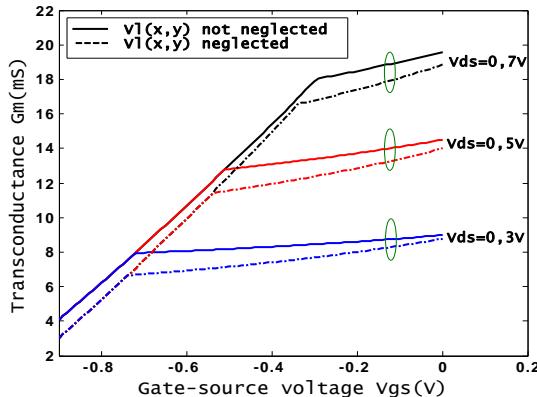

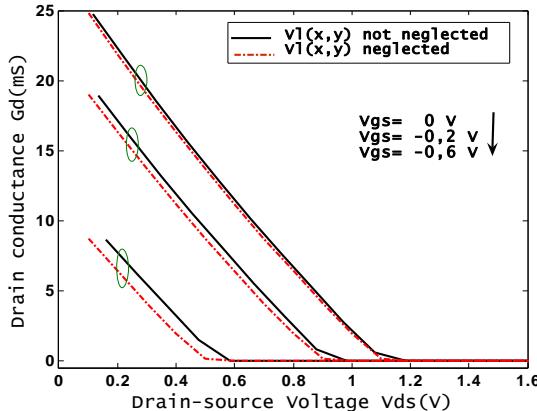

For a long channel device,  $V_g$  completely control depleting the semiconductor channel. However in short channel devices, part of channel depletion is under the control of source and drain bias. As the channel length shortens, the close proximity of the source and drain region occurs the fraction of the depletion charge in the channel. In other words, both the gate and source-drain voltages share control of the charge density below the gate. This effect is described by the figures (5), (6) and (7) were effects of  $V(0,hs)$  and  $V(L,hd)$  voltages on the drain current, transconductance and drain conductance of the GaAs MESFET are plotted with and without edge effects.

Figure 5: Variations I-V characteristics of the MESFET transistor

Figure 6 : Variation of the transconductance according to the gate voltage for the MESFET

Figure 7: Variation of the conductance according to the drain voltage for the MESFET

Figure (5) shows a comparison between the drain current characteristics with and without edge effects. From the figure it is clear seen that edge effects  $V1(x,y)$  promotes the passage of more drain current. This is mainly due to the depletion region from the source and drain which are overlapped with the channel charge. In long channel devices, this part is negligible comparing with the area of effective device channel. However, in short channel device,

this overlapped part cannot be neglected anymore and the previous approximation does not work. With the consideration of overlapped parts, the shape of the depletion charge cross-section can be described as shown in figure (1) and drain current can be calculated as expressions (20) et (22).

Such a functional dependence of the drain current suggests more involved relations for the drain conductance  $g_d$  and the transconductance  $g_m$  of the device. Like drain current, both  $g_d$  and  $g_m$  are also functions of edge effects. Figures (6) and (7) shows the changes in the values of drain conductance and transconductance caused by the voltages  $V1(0,hs)$  and  $V1(L,hd)$ , that are relatively sharper with the increase of  $Vg$  and  $Vd$

## 6. Conclusion

After we solved analytically the two-dimensional Poisson equation, we have presented the influence of edge effects for I-V characteristic, transconductance and drain conductance of the MESFET. When the depletion region extends at the drain side and source side, the depletion width is also affected by the edge effects. This has a direct influence on the characteristics of the transistor. The simulation results are well presented and discussed, the corrective term  $V1(x,y)$  gives a real approximation for the potential distributions and depletion-layer form, that are used for the calculation of the short canal device characteristics .

## References

- [1] S.Khemissi, C Kenzai and all, "Influence of physical and geometrical parameters on electrical properties of short gate GaAs MESFET's", SPQEo Vol 9 N°2, pp 34- 39, 2006.

- [2] K.N. Ratnakumar, J.D. Meindel, "Short-channel MOST threshold voltage model," IEEE J. Solid State Circuits 17 (1982) 937-947.

- [3] S.Khemissi, C. Azizi "A two-dimensional model for the potential distribution and depletion layer width of the short gate-length GaAs MESFET's", 2010 XIth International workshop on symbolic and numerical methods, modeling and applications to circuit design (SM2ACD).

- [4] M. S. Benbouza and N.Merabtine," impact of gate length on equivalent circuit elements in GaAs MESFET transistors", Journal of Electron Devices, Vol. 18, 2013, pp. 1590-1594

- [5] Sneha Kabra and all ." Two-dimensional subthreshold analysis of sub-micron GaN MESFET" Microelectronics Journal Vol 38, pp 547-555, May 2007.

- [6] Shweta Tripathi, S. jit " A two-dimensional (2d) potential distribution model for the short gate-length ion-implanted GaAs MESFETs under dark and illuminated conditions " J. Nano- Electron. Phys 3 (2011) No1, P. 868-877